CEND.jp-EMC対策・ノイズ対策の総合情報サイト

CEND.jp-EMC対策・ノイズ対策の総合情報サイト CEND.jp-EMC対策・ノイズ対策の総合情報サイト

CEND.jp-EMC対策・ノイズ対策の総合情報サイト

【パワーゲーティングの回路モデル】

電子機器に搭載される IC チップの大きな技術課題の一つが、低消費電力化である。なかでも、待機時に消費されるリーク電力は、半導体素子の微細化とともに指数関数的に増大しており 、スマートフォンやウェアラブル端末をはじめとするバッテリー駆動の機器では、IC チップのリーク電力をいかに低減するかが重要な鍵を握る。現在、IC チップのリーク電力を低減化する上で有力な技術が、パワーゲーティングと呼ばれる技術である。パワーゲーティングでは、IC チップ内部の CMOS 回路が待機状態にあるときに、その回路のみ電源を遮断し、リーク電流(サブスレショルドリーク電流)が流れないようにする。

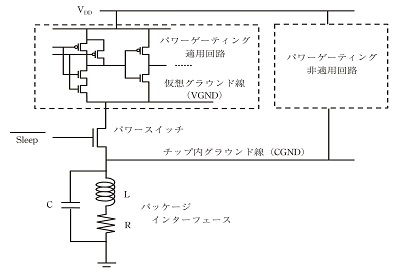

具体的には、CMOS 回路と電源の間、または CMOS 回路とグラウンドの間に、パワースイッチと呼ばれる MOSトランジスタを挿入し、CMOS 回路がアクティブ時にはパワースイッチをオンさせる一方、待機時にはパワースイッチをオフする。パワースイッチのトランジスタには、CMOS 回路のトランジスタよりしきい値(Vth)の高いトランジスタを使用することにより、パワースイッチをオフしたときのリーク電流を小さく抑えることができる。

なお、pMOS パワースイッチを電源側に挿入する場合をヘッダ方式と呼び、nMOS パワースイッチをグラウンド側に挿入する場合をフッタ方式と呼ぶ。オン時のコンダクタンスが高いことから、従来 nMOS パワースイッチが使用されてきたが、45nm のプロセス世代以降、MOS トランジスタのゲート酸化膜を通して流れるリーク電流(ゲートリーク)が顕在化したため、先端プロセスを使う ICチップでは、ゲートリークの小さい MOS のパワースイッチを使うヘッダ方式が主流になっている。

現在、実用化しているパワーゲーティング技術は、IC チップ内の大きな回路ブロック単位で電源遮断を行う技術である。例えば、ルネサスエレクトロニクスの携帯電話用 SoC(System-on-Chip) では、IC チップ内の CPU コアや DSP コアを単位としてパワーゲーティングを行い、MediaTek のスマートフォン向けSoCでは、IC チップ内に搭載した複数の CPU コアをそれぞれパワーゲーティングしている。いずれも、ある期間使わないコアは電源遮断することでリーク電力をカットしている。

続きは『月刊EMC No.339』にて

<特集>

◇ESD/EOSの基本と実態・対策、耐性試験法

・マイクロギャップESDに伴うインパルス性ノイズの放射強度と電極接近スピード

(東北学院大学 川又憲)

・静電気放電イミュニティ試験を正しく実施するための実験的解説

(㈱ノイズ研究所 石田武志)

・最新電子機器で発生する非直撃的なEOS/ESD事象と対策

(㈱インパルス物理研究所 本田昌實)

・放電現象からみたシステムESD試験の基本的問題点について

((一財)日本電子部品信頼性センター 田中政樹)

<Technology>

・MIMO方式を採用した船舶レーダの干渉対策

(日本無線㈱ 時枝幸伸)

・EMCを低減するベクトル合成を用いたワイヤレス給電法

(静岡理工科大学 郡武治)

・UPSの活用による電源ノイズ対策事例

(オムロン㈱ 林昭)

・導電性ペーストによる小型船舶のレーダー反射率向上

(国立研究法人 海上技術安全研究所 藤本、穴井、山根、村上、西崎、白石)

・ICチップの低消費電力化とオンチップノイズ低減化技術

(芝浦工業大学 宇佐美公良)

・医療環境における高速電力線搬送通信(PLC)の導入実験とEMC

(佐賀大学 花田英輔、東京医療保健大学 石田開)

<実践講座>

・ビル・工場における接地システム設計の知識 [Ⅰ]

(関東学院大学 高橋健彦)

・EMC測定・試験のポイント―今更、人に聞けないEMC用語解説

⑧同軸ケーブル (電気通信大学 名誉教授 上芳夫)

⑨平衡ケーブル (電気通信大学 名誉教授 上芳夫)

⑩伝送線路 (電気通信大学 名誉教授 上芳夫)

⑪スペクトラムアナライザ(ローデ・シュワルツ・ジャパン㈱ 吉本修)

<規格・規制情報>

・IEC61000-6-5第1版

発変電所環境イミュニティ共通規格改訂のポイント

(東北学院大学 石上忍)

Copyright(C) Kagakujyoho shuppan Co., Ltd. All rights reserved.

※記事の無断転用を禁じます。