CEND.jp-EMC対策・ノイズ対策の総合情報サイト

CEND.jp-EMC対策・ノイズ対策の総合情報サイト CEND.jp-EMC対策・ノイズ対策の総合情報サイト

CEND.jp-EMC対策・ノイズ対策の総合情報サイト

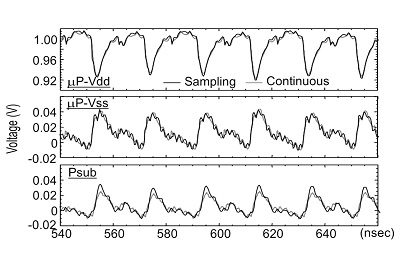

【プロセッサ動作時のオンチップ電源

ノイズ波形】

VLSI チップのダイナミックな電源ノイズは、電磁ノイズ放射による電磁環境両立性(ElectromagneticCompatibility, EMC)の問題の直接的な原因となる。他方、VLSI チップを搭載したプリント基板に外部から電磁ノイズが到来し、これが VLSI チップの電源配線に流れ込み、不具合を引き起こすノイズ干渉も問題である。VLSI チップが発生する(あるいは作用する)電源ノイズの予測と低減・回避は、VLSI チップを応用する電子システムの設計において本質的な技術課題となっている。本稿では、オンチップのノイズ観測技術およびチップレベルのノイズ解析技術について説明し、VLSI の電源ノイズに関する知見を紹介する。

チップ内部の電源ノイズや基板ノイズをチップ内部で観測するオンチップノイズモニタ技術が確立されている。本技術により、チップの実動作環境における VLSI 回路の内部ノイズを観測できる。すなわち、チップ内各所の電源ノイズやグラウンドノイズの発生、伝播、回路への影響の様子を観測することで、VLSI のノイズ問題について見通しの良い理解が得られる。ここで、実動作環境とは、チップがパッケージングされ、かつプリント基板上にマウントされた状態である。ところで、このようなノイズ観測はチップ本来の機能では無く、モニタ機構が消費するシリコン面積やピン数はできるだけ小さい事が望ましい。

ソースフォロワにより、LSIチップの基盤電位や回路内部の電源配線、グラウンド配線の電位変動を検出する。コンパレータにより、ソースフォロワの出力電圧を外部から与える基準ステップ電圧と逐次比較することで、離散化する。また、オフチップのデータ処理系において、コンパレータの出力データ例からソースフォロワの出力電圧値を読み取ることで、ノイズの時間波形を抽出する。本モニタ回路は測定対象となるデジタル回路に同期動作をしながら、デジタル回路の動作ノイズ波形を等価サンプリング原理により捕捉する。このようなノイズ観測回路をLSIチップに複数個搭載することで、チップ内各部のノイズ発生量を定量的に評価できる。

続きは『月刊EMC No.299』にて

<特集>

◇宅内直流給電技術の動向と技術課題

・宅内直流給電の動向とEMC・接地の課題

(NTT環境エネルギー研究所 秋山佳春、加藤潤、高田英俊)

・300V以上の電圧を用いた宅内直流給電の技術の現状と課題

(シャープ㈱ 川村博史)

・『共通ACアダプター』省エネルギー基準動向と応用事例

(SMK㈱ 飴井俊裕)

<Technology>

・EMC性能強化 電磁シールド樹脂複合材料

(帝人化成㈱ 友田琢也)

・電波干渉を避ける無線型監視システム

(㈱日立製作所 水垣健一)

・SiC-MOSFETインバータのEMIノイズ特性

(芝浦工業大学 齊藤真)

・VLSI電源ノイズの観測・解析と究明

(神戸大学 永田真)

<規格・規制情報>

・一体形又は分離形のシグナルコンディショナ付き

トランデューサの試験配置、動作条件、性能評価基準

(㈱堀場製作所 青山剛士)

・絶縁監視機器及び絶縁故障場所検出用装置の試験配置、動作条件及び性能評価基準

(㈱エヌエフ回路設計ブロック 三宮隆志)

・製品安全とEMC

(㈱エークリエイト 竹牟禮昭示)

<実践講座>

・熱流体シミュレーションを用いた電子機器の熱解析のための電子部品のモデル化

~その2:チョークコイルのモデル化~

(コーセル㈱ 小泉雄大)

<インフォメーション>

・今、そこにあるEMC「スマートグリッドシステムのEMC」

・今、そこにあるEMC「EMCシミュレーション」

・どうなる!「自動車と人体防護」

・日本の国際標準化活動 攻勢に向けて

・エレベータの安全・安心は電気設計が握る

・製造メーカー責任はどうなるか?

Copyright(C) Kagakujyoho shuppan Co., Ltd. All rights reserved.

※記事の無断転用を禁じます。