CEND.jp-EMC対策・ノイズ対策の総合情報サイト

CEND.jp-EMC対策・ノイズ対策の総合情報サイト CEND.jp-EMC対策・ノイズ対策の総合情報サイト

CEND.jp-EMC対策・ノイズ対策の総合情報サイト

【アナログ回路ダイサイズと

技術世代の寸法の関係】

集積回路(LSI)は、スケーリング即ちトランジスタの寸法を縮小することにより、その性能を向上させてきた。現在に至ってもトランジスタの最小設計寸法は縮小を続けているが、シリコン基板上に平面的に配置されるバルクプレーナ MOSFET では基板下部からの漏れ電流を抑えることが困難になり、22nm技術世代より直立した薄いシリコン(fin)をチャネルとして用いる FinFET の採用が始まった。また近年、スマホ、タブレット等無線接続を前提とする携帯型情報端末の普及を受け、システム LSI にはデジタル回路だけで無くアナログ回路も混載され、機器のコンパクト化、低コスト化に貢献している。

LSI を設計する上でプラットフォームとなる CMOSデバイスは、スケーリングを進めることにより性能向上、低コスト化を果たしてきているが、システムLSI ではスケーリングがアナログ回路に与える影響も考慮する必要がある。アナログ回路のスケーリングを進める上で注意すべき重要な点として、フリッカノイズが挙げられる。

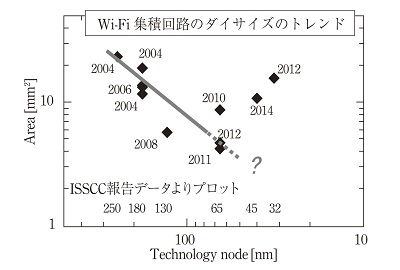

学会レベルで報告されている Wi-Fi 集積回路のダイサイズと、使用されている技術世代寸法の関係より、65nm 技術世代あたりで、ダイサイズがあまり縮小しなくなっている。より寸法の小さい技術世代への移行することで、トランジスタの性能向上とダイサイズの縮小によるコスト低減が期待されるが、アナログ回路面積の縮小が困難になることで相対的にアナログ回路のコストが増加してしまう懸念がある。このため、同じデバイス寸法当たりのノイズレベルを下げるデバイス技術が重要となってくる。

ところで、22nm世代より導入が開始されたFinFETでは、漏れ電流の低減だけで無く、ノイズレベルの点からも有利であると期待されている。バルクプレーナ MOSFETでは、比較的高濃度にドーピングされた基板を反転させるため、チャネル表面には強い電界が加わっている。

このため、キャリアである電子はゲート絶縁膜の極めて近くを流れる。フリッカノイズは、ゲート絶縁膜 / シリコン界面のトラップで不規則に捕獲・放出される電荷の影響をキャリアが受けることにより発生する。ゲート絶縁膜の極めて近くを流れるキャリアはトラップ電荷の影響を強く受け、より大きなフリッカノイズを発生させる。

続きは『月刊EMC No.335』にて

<特集>

◇国内主要メーカー&取り扱い企業群50社 2016年版 高信頼/EMC関連製品一覧

▼EMC 部品・製品編

EMI除去フィルタ/ノイズ防止トランス/自動定電圧装置/無停電電源装置/雷対策機器/サージアブソーバ

▼静電気対策関連製品編

ESD対策部品・製品

▼シールド・吸収材編

電磁波シールド材/磁気シールド/熱拡散材/シールドルーム/電磁波吸収体

▼試験装置・設備編

試験器/試験システム/アンテナ/アンテナ昇降機/電波暗室/計測/シールドボックス/TEMセル/ ターンテーブル

▼設計ツール編

シミュレーションソフトウェア

<Technology>

・モータ駆動ケーブルに誘起するコモンモード電圧対策法

(九州工業大学 桑原伸夫)

・先端CMOS トランジスタにおけるフリッカノイズ対策

(国立研究開発法人 産業技術総合研究所 松川貴、柳永勛、福田浩一、大内真一、昌原明植)

<実践講座>

・EMC測定・試験のポイント-今更、人に聞けないEMC用語解説

連載の開始によせて

(東京都市大学名誉教授 徳田正満)

・EMC測定・試験のポイント-今更、人に聞けないEMC用語解説①

EMC(電磁両立性)

(東京都市大学名誉教授 徳田正満)

Copyright(C) Kagakujyoho shuppan Co., Ltd. All rights reserved.

※記事の無断転用を禁じます。