CEND.jp-EMC対策・ノイズ対策の総合情報サイト

CEND.jp-EMC対策・ノイズ対策の総合情報サイト CEND.jp-EMC対策・ノイズ対策の総合情報サイト

CEND.jp-EMC対策・ノイズ対策の総合情報サイト

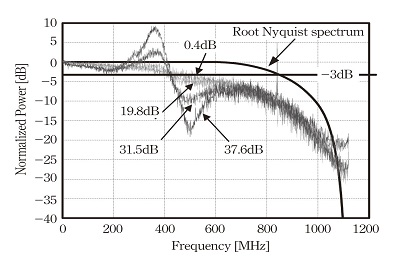

【VGA+ADC の周波数特性(10MHz 入力で正規化)】

デジタル回路とアナログ回路を同一チップに混載したアナログ・デジタル混載集積回路は様々な用途に広く用いられており、今日ではデジタル回路のみの集積や、アナログ回路のみの集積の方が珍しくなっている。したがって、集積回路技術の中心になったといっても過言ではない。アナログ・デジタル混載集積回路が開発されだしたのは 1990 年代からであるが、当初はデジタル回路からの回り込みノイズの影響を受け、アナログ特性が劣化した。

ノイズを低減するための設計ツールが開発されたが、状況を劇的に改善したのはシリコン基板とトランジスタをほぼ完全に隔離するトリプルウエル(ディープ N ウエルとも言う)の導入である。それまではアナログ回路とデジタル回路の基板が共通であり、デジタル回路からのノイズが基板を介して直接アナログ回路に回り込んでいたため、アナログ特性の劣化が激しかった。しかしながらトリプルウエルの導入により基板からのノイズの回り込みが劇的に減少したため、アナログ特性の劣化は大幅に緩和された。

1990年代はトリプルウエルはコストアップ要因であったので使用が限定されていたが、2000 年代は配線工程のコストが増加したため、ウエルの追加はコストには殆ど影響を与えないようになった。システム全体の集積の観点からアナログ回路の集積が始まり、今日ではアナログ・デジタル混載集積回路が主流になったので、トリプルウエルは CMOS プロセスの標準になっている。

トリプルウエルの導入により、アナログ特性の深刻な劣化は少なくなったが、それでもチップ内での結合、パッケージにおける結合により、アナログ特性の劣化が見られ、機器の性能向上の妨げになっている。しかしながら、原因の特定や対策効果の確認が困難であり、定量的に解析されたものは極めて少ない。いわゆる失敗例を公表する困難さもあり、発表事例は極めて少ないのが現状である。

本稿も学術論文としては科学的手法の適用が不十分であり、掲載をためらうところもあるが、事例紹介として、アナログ・デジタル混載集積回路開発者の皆さんにとって参考になれば幸いである。取り上げる事例はいずれも総務省プロジェクトにおけるミリ波トランシーバ集積回路の開発で発生したものである。信号帯域は 200 MHz ~ 1.0 GHz と広帯域で、標本化周波数が 400 MS/s ~ 2.3 GS/s と高速のA/D・D/A 変換器を搭載するアナログ・デジタル混載集積回路である。

続きは『月刊EMC No.346』にて

<特集>

◇EMCC シンポジウム

・医療機関における 適正な電波利用環境の構築を目指して

<Technology>

・ハイブリッドコイルによる照明/AV/OA 機器のノイズ対策

(NEC トーキン(株) 板谷道隆)

・インバータとブリッジレスPFC 回路の伝導ノイズ低減法

(九州大学 庄山正仁)

・高速・広帯域アナログ・デジタル混載集積回路におけるノイズ課題

(東京工業大学工学院 松澤昭、宮原正也)

・接触力計測のためのマイクロメカニカルセンサの実装とノイズ低減

(新潟大学 寒川雅之)

<Information>

・IEC 1906 賞受賞

マルチメディア機器のEMC 規格制定に貢献 実験に基づく寄与文書を評価

(PFUテクノコンサル(株) 千代島敏夫)

<規格・規制情報>

・IEC61643-351:2016 Ed.1.0 解説

サージアイソレーショントランスフォーマポイント解説

((株)NTTファシリティーズ) 佐藤秀隆)

<実践講座>

・製品の信頼性を高めるLSI のEMC 設計 ③

用途別半導体集積回路の電磁両立性設計(1)

(ローム(株) 稲垣亮介)

Copyright(C) Kagakujyoho shuppan Co., Ltd. All rights reserved.

※記事の無断転用を禁じます。